حاسب بمجموعة مخفضة من التعليمات

هذه المقالة may be too technical for most readers to understand. Please improve هذه المقالة to make it understandable to non-experts, without removing the technical details. (October 2016) |

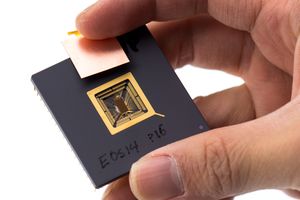

حاسب بمجموعة مخفضة من التعليمات reduced instruction set computer، أو ريسك RISC (/rɪsk/)، وهو عبارة عن حاسب به مجموعة من التعليمات الصغيرة والتي تم تحسينها بشكل كبير، بدلاً من المجموعة الأكثر تخصصًا التي توجد غالبًا في أنواع أخرى من البنى، مثل حاسب مجموعة التعليمات المعقدة (CISC).[1] السمة المميزة الرئيسية لبنية ريسك RISC هي وجود مجموعة التعليمات المُحسّنة بعدد كبير من المسجلات و نواقل التعليمات المنتظمة للغاية، مما يسمح بعدد منخفض من دورات الساعة لكل تعليمة (CPI). ميزة أخرى شائعة لـ ريسك RISC هي بنية التحميل / التخزين ،[2] حيث يتم الوصول إلى الذاكرة من خلال تعليمات محددة وليس كجزء من معظم التعليمات في المجموعة.

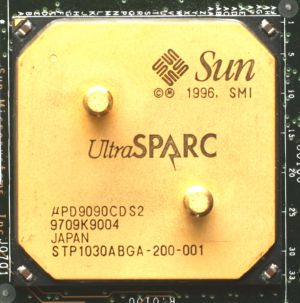

على الرغم من أن عددًا من أجهزة الحاسب من الستينيات والسبعينيات قد تم تحديدها على أنها رائدة في RISCs، إلا أن المفهوم الحديث يعود إلى الثمانينيات. وخاصة، بوجود مشروعان في جامعة ستانفورد و جامعة كاليفورنيا، بيركلي أكثر ارتباطًا بتعميم هذا المفهوم. ميپس ستانفورد سوف يتم تسويقه باعتباره بنية ميپس الناجحة، بينما أعطت بيركلي ريسك اسمها للمفهوم بأكمله وتم تسويقه على أنه SPARC. ونجاح آخر من هذا العصر كان جهود IBM التي أدت في النهاية إلى بنية مجموعة تعليمات IBM POWER ، PowerPC ، و Power ISA. مع نضوج هذه المشاريع، ازدهرت مجموعة متنوعة من التصميمات المماثلة في أواخر الثمانينيات وخاصة أوائل التسعينيات، مما يمثل قوة رئيسية في سوق محطة عمل يونكس وكذلك بالنسبة لـ المعالج المدمج في طابعات الليزر و أجهزة التوجيه ومنتجات مماثلة.

تتضمن الأنواع العديدة لتصميمات ريسك ARC ، Alpha ، Am29000 ، ARM ، Atmel AVR ، Blackfin ، i860 ، i960 ، M88000 ، ميپس ، PA-RISC و Power ISA (بما في ذلك PowerPC) و RISC-V و SuperH و SPARC. إن استخدام معالجات بنية ARM في الهواتف الذكية و الحاسب اللوحي مثل أجهزة آي پاد و أندرويد قد وفر قاعدة واسعة للمستخدمين للأنظمة القائمة على ريسك RISC. وتُستخدم معالجات ريسك RISC أيضًا في أجهزة الحاسب الفائقة ، مثل فوجاكو ، وهو اعتبارا من يونيو 2020[تحديث]، أسرع حاسب فائق في العالم.[3]

تاريخ و تطوير

استندت بيركلي ريسك Berkeley RISC إلى اكتساب الأداء من خلال استخدام خطوط النقل والاستخدام القوي لتقنية تُعرف باسم نوافذ المسجلات.[4][5] في وحدة المعالجة المركزية التقليدية، تمتلك واحدها عددًا صغيرًا من المسجلات، ويمكن لأي برنامج استخدام أي مسجل في أي وقت. في وحدة المعالجة المركزية (CPU) ذات نوافذ المسجلات، يوجد عدد كبير من المسجلات، على سبيل المثال، 128، ولكن لا يمكن للبرامج استخدام سوى عدد صغير منها، على سبيل المثال، ثمانية، في وقت واحد. يمكن للبرنامج الذي يقيد نفسه إلى ثمانية مسجلات لكل إجراء أن يجعل استدعاءات الإجراء سريعةً جدًا: يقوم الاستدعاء ببساطة بتحريك النافذة "لأسفل" بمقدار ثمانية، إلى مجموعة المسجلات الثمانية المستخدمة بواسطة هذا الإجراء، وتحرك تعليمة العودة من الإجراء النافذة مرة أخرى.[6]قام مشروع بيركلي ريسك Berkeley RISC بتقديم معالج RISC-I في عام 1982. ويتألف من 44420 ترانزستورًا فقط (مقارنة بمتوسط حوالي 100000 في تصميمات أحدث لعهد CISC) كان لدى RISC-I 32 تعليمة فقط، ومع ذلك فقد تفوقت تمامًا على أي تصميم آخر أحادي الشريحة. تبعوا ذلك مع 40760 ترانزستور، 39 تعليمة RISC-II في عام 1983، والتي كانت أسرع بثلاث مرات من RISC-I.[5]

تطور مشروع ميپس من دورة للدراسات العليا بواسطة جون إل. هنِسي في جامعة ستانفورد في عام 1981، مما تم التوصل لنظام يعمل في عام 1983، ويمكنه تشغيل برامج بسيطة بحلول عام 1984.[7]أكد منهج ميپس على دورة نبضات ساعة صارمة واستخدام خط النواقل، والتأكد من أنه يمكن تشغيله "بالكامل" قدر الإمكان.[7]وقد تم اتباع نظام ميپس بواسطة MIPS-X وفي عام 1984 قام هنِسي وزملاؤه بتشكيل ميپس كومپيوتر سستمز.[7][8] فقد نتج عن المشروع التجاري بنية جديدة كانت تسمى أيضًا ميپس و معالج R2000 في عام 1985.[8]

في أوائل الثمانينيات من القرن الماضي، أحاطت شكوك كبيرة بمفهوم ريسك RISC، ولم يكن من المؤكد ما إذا كان يمكن أن يكون له مستقبل تجاري، ولكن بحلول منتصف الثمانينيات، نضجت مفاهيمها بما يكفي ليتم اعتبارها مجدية تجاريًا.[9][7]في عام 1986 بدأت هيولت پاكارد باستخدام التنفيذ الأولي لـ PA-RISC في بعض أجهزة الحاسب الخاصة بهم.[9] في غضون ذلك، أصبح جهد و تأثير بيركلي ريسك معروفًا جدًا لدرجة أنه أصبح في النهاية اسمًا للمفهوم بأكمله وفي عام 1987 بدأت سَن للأنظمة الدقيقة بشحن و توريد أنظمتها باستخدام معالج SPARC، الذي يعتمد بشكل مباشر على نظام بيركلي RISC-II.[9][10]

تنسب اللجنة الحكومية الأمريكية المعنية بالابتكارات في مجال الحوسبة والاتصالات قبولها لمفهوم ريسك إلى نجاح نظام SPARC.[9]جدد نجاح SPARC الاهتمام داخل شركة IBM، التي أصدرت أنظمة ريسك جديدة بحلول عام 1990 وبحلول عام 1995 كانت معالجات ريسك أساس صناعة المخدمات بقيمة 15 مليار دولار.[9]

منذ عام 2010، تم تطوير بنية مجموعة التعليمات ذات المصدر المفتوح (ISA) RISC-V ، في جامعة كاليفورنيا، بيركلي، لأغراض البحث و كبديل مجاني لمعايير التدقيق الدولية المسجلة الملكية. اعتبارًا من عام 2014، تم إصلاح الإصدار 2 من مساحة المستخدم ISA.[11] تم تصميم ISA لتكون قابلة للتوسعة من نواة مجردة كافية ومناسبة لمعالج صغير مدمج إلى استخدام الحاسب الفائق والحوسبة السحابية مع ملحقات ومعالجات مشتركة محددة ومصممة للشرائح. تم اختباره في تصميم السليكون باستخدام SoC ROCKET والذي يتوفر أيضًا كمولد معالج مفتوح المصدر بلغة CHISEL.

الخصائص وفلسفة التصميم

هذا section يحتاج المزيد من الأسانيد للتحقق. (March 2012) (Learn how and when to remove this template message) |

فلسفة مجموعة التعليمات

إن سوء الفهم الشائع لعبارة "حاسب بمجموعة مخفضة من التعليمات" هو الفكرة الخاطئة بأن التعليمات يتم التخلص منها ببساطة، مما يؤدي إلى مجموعة أصغر من التعليمات.[12] في الواقع، على مر السنين، تطورت مجموعات تعليمات ريسك RISC من ناحية الحجم، واليوم العديد منها لديها مجموعة أكبر من التعليمات من العديد من وحدات المعالجة المركزية CISC.[13][14] تحتوي بعض معالجات ريسك RISC مثل PowerPC على مجموعات تعليمات كبيرة مثل CISC IBM System / 370 ، على سبيل المثال؛ على العكس من ذلك ، فإن DEC PDP-8 - من الواضح أن وحدة المعالجة المركزية لديها هي CISC لأن العديد من تعليماتها تتضمن وصولاً متعدداً إلى الذاكرة- أي لديها فقط 8 تعليمات أساسية وبعض التعليمات الموسعة.[15] المقصود من المصطلح "مخفض" في هذه العبارة هو وصف حقيقة أن مقدار العمل الذي تنجزه أي تعليمة مفردة قد انخفض - دورة ذاكرة بيانات واحدة على الأكثر- مقارنةً بـ "التعليمات المعقدة" لوحدات المعالجة المركزية CISC التي قد يتطلب ذلك عشرات من دورات ذاكرة البيانات من أجل تنفيذ تعليمة واحدة.[16] على وجه الخصوص ، تحتوي معالجات RISC عادةً على تعليمات منفصلة للإدخال / الإخراج ومعالجة البيانات.[17]

يتم تفضيل أحيانًا المصطلح بنية التحميل / التخزين.

تشكيل التعليمات

تحتوي معظم بنى ريسك RISC على تعليمات ذات طول ثابت (عادةً 32 بت) وتشفير بسيط، مما يبسط الاستدعاء المسبق، وفك التشفير، وإصدار تعليمات منطقية إلى حد كبير. يتمثل أحد عيوب التعليمات ذات 32 بت في تقليل كثافة التعليمات البرمجية، والتي تعد خاصية أكثر سلبية في الحوسبة المضمنة مقارنة بمحطة العمل وأسواق المخدمات، وقد تم تصميم بنى ريسك RISC في الأصل للخدمة. لمعالجة هذه المشكلة، هناك العديد من البنى ، مثل ARM ، Power ISA ، ميپس ، RISC-V ، و Adapteva Epiphany ، لها تنسيق تعليمات اختياري قصير ومختصر الميزات أو ميزة ضغط التعليمات. ويتبع SH5 هذا النمط أيضًا، وإن كان قد تطور في الاتجاه المعاكس، حيث أضاف إرشادات وسائط أطول إلى تشفير 16 بت الأصلي.

استخدام الأجهزة

لأي مستوى معين من الأداء العام، عادةً ما يكون لشريحة ريسك RISC عدد أقل بكثير من الترانزستورات المخصصة للمنطق الأساسي الذي سمح للمصممين في الأصل بزيادة حجم مجموعة التسجيل وزيادة التطابق الداخلي.

تشمل الميزات الأخرى لبنى ريسك RISC ما يلي:

- يقترب متوسط إنتاجية المعالج من 1 تعليمة لكل دورة

- تنسيق تعليمات موحد، باستخدام كلمة واحدة مع كود التشغيل في نفس مواضع البت من أجل فك تشفير أبسط

- يمكن استخدام جميع مسجلات الأغراض العامة بالتساوي كمصدر / وجهة في جميع التعليمات، وتبسيط تصميم المحول (غالبًا ما يتم الاحتفاظ بمسجلات الفاصلة العائمة منفصلة)

- وضع عنونة بسيط مع عنونة معقدة تؤديها تسلسلات التعليمات

- القليل من أنواع البيانات في الأجهزة (بدون سلسلة بايت أو BCD ، على سبيل المثال)

من المرجح أيضًا أن تتميز تصميمات ريسك RISC من نموذج ذاكرة هارڤارد ، حيث يتم فصل تدفق التعليمات وتدفق البيانات من الناحية المفاهيمية؛ هذا يعني أن تعديل الذاكرة حيث يتم الاحتفاظ بالشفرة قد لا يكون له أي تأثير على التعليمات التي ينفذها المعالج (لأن وحدة المعالجة المركزية لديها تعليمات وبيانات ذاكرة التخزين المؤقت منفصلة)، على الأقل حتى يتم إصدار تعليمات مزامنة خاصة. على الجانب الإيجابي، يسمح هذا بالوصول إلى كلا الذاكرتين المؤقتتين في وقت واحد، مما يؤدي غالبًا إلى تحسين الأداء.

تشترك العديد من تصميمات ريسك RISC الأولية أيضًا في خاصية امتلاك فتحة تأخير الفرع، وهي مساحة تعليمات بعد قفزة أو فرع مباشرةً. يتم تنفيذ التعليمات الموجودة في هذه المساحة، سواء تم أخذ الفرع أم لا (بمعنى آخر، تأخر تأثير الفرع). تحافظ هذه التعليمات على ALU لوحدة المعالجة المركزية مشغولة للوقت الإضافي اللازم عادةً لأداء الفرع. في الوقت الحاضر، تعتبر فتحة تأخير الفرع أحد الآثار الجانبية الغير ملائمة لإستراتيجية معينة لتنفيذ بعض تصميمات ريسك RISC، وتصاميم ريسك RISC الحديثة تتخلص منها عمومًا (مثل PowerPC والإصدارات الأحدث من SPARC و ميپس).[بحاجة لمصدر]

بعض الجوانب المنسوبة إلى أول ريسك RISC - التصميمات "المسماة" حول 1975 تتضمن الملاحظات التي تشير إلى أن المحول المقيد بالذاكرة في ذلك الوقت لم يتمكن في كثير من الأحيان من الاستفادة من الميزات التي تهدف إلى تسهيل التجميع "اليدوي" للترميز، وهذا وضع العنونة المعقد يستغرق العديد من الدورات لأدائه بسبب الوصول إلى الذاكرة الإضافية المطلوبة. وقد قيل أن مثل هذه الوظائف يمكن أداؤها بشكل أفضل من خلال تسلسل من التعليمات الأبسط إذا كان هذا يمكن أن ينتج عنه تطبيقات صغيرة بما يكفي لترك مساحة للعديد من المسجلات، مما يقلل من عدد العمليات البطيئة للوصول إلى الذاكرة. في هذه التصميمات البسيطة، تكون معظم التعليمات ذات طول موحد وبنية متشابهة، وتقتصر العمليات الحسابية على مسجلات وحدة المعالجة المركزية وذاكرة الوصول إلى تعليمات التحميل و التخزين المنفصلة فقط. تتيح هذه الخصائص موازنة أفضل لـ مراحل النقل من ذي قبل، مما يجعل نواقل ريسك RISC أكثر كفاءة بشكل ملحوظ ويتيح ترددات ساعة أعلى.

جاء دافع آخر لكل من ريسك RISC والتصميمات الأخرى من القياسات العملية في برامج العالم الحقيقي. لخص أندرو تانينباوم العديد من تلك التصميمات، موضحًا أن المعالجات غالبًا ما كانت كبيرة الحجم. على سبيل المثال، أظهر أن 98٪ من جميع الثوابت في برنامج ما تتناسب مع 13 بت ثانية ، ومع ذلك فقد خصصت العديد من تصميمات وحدة المعالجة المركزية 16 أو 32 بتًا لتخزينها. يشير هذا إلى أنه لتقليل عدد مرات الوصول إلى الذاكرة، يمكن للآلة ذات الطول الثابت تخزين الثوابت في أجزاء غير مستخدمة من كلمة التعليمات نفسها، بحيث تكون جاهزة على الفور عندما تحتاج إليها وحدة المعالجة المركزية (مثل المعالجة الفورية في تصميم تقليدي). هذا يتطلب كود التشغيل صغير من أجل ترك مساحة لثابت بحجم معقول في كلمة تعليمات 32 بت.

نظراً لأن العديد من برامج العالم الحقيقي تقضي معظم زمنها في تنفيذ عمليات بسيطة، فقد قرر بعض الباحثين التركيز على جعل هذه العمليات بأسرع ما يمكن. معدل الساعة لوحدة المعالجة المركزية محدودة بالزمن الذي يستغرقه تنفيذ أبطأ "عملية فرعية" من أي تعليمة؛ يؤدي تقليل زمن الدورة غالبًا إلى تسريع تنفيذ التعليمات الأخرى.[18]أدى التركيز على "التعليمات المخفضة" إلى تسمية الآلة الناتجة بـ "حاسب بمجموعة مخفضة من التعليمات" ريسك (RISC). كان الهدف هو جعل التعليمات بسيطة للغاية بحيث يمكن "بسهولة" أن تكون موصلة بالنواقل ، من أجل تحقيق إنتاجية ساعة واحدة عند ترددات عالية.

لاحقًا، لوحظ أن إحدى أهم خصائص معالجات ريسك RISC هي أن الذاكرة الخارجية لا يمكن الوصول إليها إلا من خلال تعليمات تحميل أو تخزين. اقتصرت جميع التعليمات الأخرى على المسجلات الداخلية. أدى هذا إلى تبسيط العديد من جوانب تصميم المعالج: السماح للتعليمات بأن تكون بطول ثابت، وتبسيط النواقل ، وعزل وحدات المنطق للتعامل مع التأخير في إكمال الوصول إلى الذاكرة (فقدان ذاكرة التخزين المؤقت، وما إلى ذلك) لتعليمتين فقط. أدى ذلك إلى الإشارة إلى تصميمات RISC باسم بنى تحميل / تخزين.[19]

مقارنة مع البنى الأخرى

تم تصميم بعض وحدات المعالجة المركزية خصيصًا بحيث تحتوي على مجموعة صغيرة جدًا من التعليمات – ولكن هذه التصميمات مختلفة تمامًا عن تصميمات ريسك RISC الكلاسيكية، لذلك تم إعطاؤها أسماء أخرى مثل حاسب بمجموعة مصغرة من التعليمات (MISC) أو بنية تشغيل وسائط النقل للتعليمات (TTA).

حققت بنى ريسك RISC نجاحات قليلة تقليديًا في أسواق أجهزة الحاسب المكتبية وأسواق المخدمات، حيث تظل الأنظمة الأساسية القائمة على x86 هي بنية المعالج المهيمنة. ومع ذلك، قد يتغير هذا، حيث يتم تطوير المعالجات القائمة على ARM لأنظمة عالية الأداء.[20] أصدرت الشركات المصنعة بما في ذلك كاڤيوم و AMD و معالجات مخدم كوالكوم تستند إلى بنية ARM.[21][22]فقد دخلت ARM في شراكة أخرى مع كراي في عام 2017 لإنتاج كمبيوتر فائق قائم على ARM.[23]على سطح المكتب، أعلنت مايكرو سوفت أنها تخطط لدعم إصدار الحاسب الشخصي من وندوز 10 على الأجهزة القائمة على كوالكوم سناپ دراگن في عام 2017 كجزء من شراكتها مع كوالكوم. ستدعم هذه الأجهزة تطبيقات وندوز المجمعة لـ x86 32 بت عبر معالج x86 المحاكي الذي يحول كود x86 32 بت إلى كود ARM64.[24][25]وقد أعلنت شركة آپل أنها ستحول أجهزة الحاسب المكتبية والمحمولة ماك من معالجات إنتل إلى SoCs مطورة داخليًا تعتمد على ARM64 تسمى آپل سليكون. ستكون أجهزة ماك المزودة بـ آپل سليكون قادرة على تشغيل ثنائيات x86-64 باستخدام Rosetta 2، محول x86-64 إلى ARM64.[26]

خارج ساحة سطح المكتب، ومع انتشار بنية ARM RISC على نطاق واسع في الهواتف الذكية والأجهزة اللوحية والعديد من أشكال الأجهزة المدمجة. كما هو الحال أيضًا منذ معالجات پنتيوم Pro (P6)، قامت معالجات إنتل x86 بتحويل تعليمات x86 CISC داخليًا إلى واحد أو أكثر من عمليات دقيقة مثل ريسك RISC، وجدولة العمليات الصغيرة وتنفيذها بشكل منفصل.[27]

في حين اختلفت تصميمات RISC الأولية بشكل كبير عن تصميمات CISC المعاصرة، بحلول عام 2000، كان من المستحيل تقريبًا تمييز وحدات المعالجة المركزية الأعلى أداءً في خط RISC عن وحدات المعالجة المركزية الأعلى أداءً في خط CISC.[28][29][30]

استخدام بنية ريسك RISC

تُستخدم الآن بنى ريسك RISC عبر مجموعة من الأنظمة الأساسية، من الهواتف الذكية و الحواسب اللوحية إلى بعض أجهزة الحواسب الفائقة الأسرع في العالم مثل سوميت، الأسرع على الإطلاق من قائمة TOP500 اعتبارا من نوفمبر 2018[تحديث].[31]

الجوالات و الأنظمة ذات الجودة المنخفضة

بحلول بداية القرن الحادي والعشرين، اعتمدت غالبية الأنظمة ذات الجودة المنخفضة والجوالات على بنى ريسك RISC.[32]تتضمن الأمثلة:

- تهيمن بنية ARM على سوق الأنظمة المدمجة منخفضة الطاقة ومنخفضة التكلفة (عادةً 200–1800 ميگاهرتز في عام 2014). يتم استخدامه في عدد من الأنظمة مثل معظم الأنظمة القائمة على أندرويد ، آپل آيفون و iPad ، مايكروسوفت وندوز فون (سابقًا وندوز موبايل) و RIM وأجهزة ننتندو گيم بوي المتقدمة و DS و 3DS و مفاتيح كهربائية ، راسپيري پاي، إلخ.

- تم استخدام PowerPC الخاص بـ IBM في ألعاب گيم كيوب و لوحات وي و پلاي ستيشن 3 و إكس بوكس 360 و وي يو.

- تم استخدام خط ميپس (عند نقطة واحدة مستخدمة في العديد من أجهزة حاسب SGI) في پلاي ستيشن ، پلاي ستيشن 2 ، ننتندو 64 ، پلاي ستيشن المحمولة وحدات التحكم في الألعاب ، و بوابات داخلية مثل سلسلة Linksys WRT54G.

- هيتاشي SuperH ، المستخدمة على نطاق واسع في سيگا Super 32X ، ساتيرن و دريم كاست ، تم تطويره وبيعه الآن بواسطة رنِساس باعتباره SH4.

- تستخدم Atmel AVR في مجموعة متنوعة من المنتجات تتراوح من أجهزة التحكم المحمولة ل إكس بوكس ومنصة متحكم أردوينو مفتوحة المصدر إلى سيارات BMW.

- RISC-V ، مصدر مفتوح خامس من بيركلي ريسك Berkeley RISC ISA، مع مساحة العنوان 32 أو 64 بت، وهو عدد صحيح صغير من مجموعة التعليمات، و ISA تجريبي "مضغوط" بسبب كثافة الكود ومصمم لملحقات الأغراض القياسية والخاصة.

محطات العمل، مخدمات، و الحواسيب الفائقة

- معالجات من تصميم آپل استنادًا إلى بنية ARM ستستخدمها تشكيلة آپل لأجهزة الحواسيب المكتبية والمحمولة بعد الانتقال من معالجات إنتل.[33]

- ميپس ، من قِبل سليكون گرافكس (التي توقفت عن صنع الأنظمة المستندة إلى ميپس في عام 2006).

- SPARC، من قِبل أوراكل (سابقًا Sun للأنظمة الدقيقة) ، و فيوجتسو.

- بنية مجموعة تعليمات IBM POWER ،من IBM PowerPC ، و Power ISA ، الأكثر شهرة لاستخدامها على العديد من طرازات حاسب ماكنتوش قبل الانتهاء من الانتقال إلى معالجات إنتل,[34]وفي العديد من أجهزة الحواسيب الفائقة والمخدمات ومحطات العمل متوسطة المدى لشركة IBM.

- Hewlett-Packard الخاص بـ PA-RISC ، المعروف أيضًا باسم HP-PA (تم إيقافه في نهاية عام 2008).

- Alpha ، تُستخدم في حواسيب أحادية اللوحة ومحطات العمل والمخدمات وأجهزة الحواسيب الفائقة من شركة المعدات الرقمية ، ثم كومپاك وأخيراً HP (تم إيقافها اعتبارًا من 2007).

- RISC-V ، مصدر مفتوح من نماذج RISC ISA الخامسة من بيركلي، مع مساحات العنوان 64 أو 128 بت، ونواة العدد الصحيح ممتدة مع الفاصلة العائمة، عمليات على مستوى الذرات و معالجة المتجهات ، ومصممة لتوسيعها بتعليمات للتواصل عبر الشبكة، والإدخال / الإخراج ، ومعالجة البيانات. ويتوفر تصميم فائق السعة 64 بت ، "Rocket" ، للتنزيل.

انظر أيضاً

- Addressing mode

- Classic RISC pipeline

- Complex instruction set computer

- Computer architecture

- Instruction set architecture

- Microprocessor

- Minimal instruction set computer

المراجع

- ^ Berezinski, John. "RISC — Reduced instruction set computer". Department of Computer Science, Northern Illinois University. Archived from the original on 28 فبراير 2017.

- ^ Flynn, Michael J. (1995). Computer architecture: pipelined and parallel processor design. pp. 54–56. ISBN 0867202041.

- ^ "Japan's Fugaku gains title as world's fastest supercomputer". RIKEN. Retrieved 24 يونيو 2020.

- ^ خطأ استشهاد: وسم

<ref>غير صحيح؛ لا نص تم توفيره للمراجع المسماةPattersonDitzel - ^ أ ب خطأ استشهاد: وسم

<ref>غير صحيح؛ لا نص تم توفيره للمراجع المسماةPattersonSequin - ^ (July 1982) "Design and Implementation of RISC I" in Advanced Course on VLSI Architecture.. CSD-82-106.

- ^ أ ب ت ث Chow, Paul (1989). The MIPS-X RISC microprocessor. pp. xix–xx. ISBN 0-7923-9045-8.

- ^ أ ب Nurmi 2007, pp. 52–53

- ^ أ ب ت ث ج Funding a Revolution: Government Support for Computing Research by Committee on Innovations in Computing and Communications 1999 ISBN 0-309-06278-0 page 239

- ^ Tucker, Allen B. (2004). Computer science handbook. pp. 100–6. ISBN 1-58488-360-X.

- ^ Waterman, Andrew; Lee, Yunsup; Patterson, David A.; Asanovi, Krste. "The RISC-V Instruction Set Manual, Volume I: Base User-Level ISA version 2 (Technical Report EECS-2014-54)". University of California, Berkeley. Retrieved 26 ديسمبر 2014.

- ^ Esponda, Margarita; Rojas, Ra'ul (سبتمبر 1991). "Section 2: The confusion around the RISC concept". The RISC Concept — A Survey of Implementations. Freie Universitat Berlin. B-91-12.

{{cite book}}: Cite has empty unknown parameter:|chapterurl=(help) - ^ [Stokes, Jon "Hannibal". "RISC vs. CISC: the Post-RISC Era". Arstechnica.

- ^ Borrett, Lloyd (يونيو 1991). "RISC versus CISC". Australian Personal Computer.

- ^ Jones, Douglas W. "Doug Jones's DEC PDP-8 FAQs". PDP-8 Collection, The University Of Iowa Department of Computer Science.

- ^ Dandamudi, Sivarama P. (2005). "Ch. 3: RISC Principles". Guide to RISC Processors for Programmers and Engineers. Springer. pp. 39–44. doi:10.1007/0-387-27446-4_3. ISBN 978-0-387-21017-9.

the main goal was not to reduce the number of instructions, but the complexity

{{cite book}}: Invalid|ref=harv(help) - ^ Ambriz, Kelly (25 مايو 1999). "I/O processor for optimal data transfer". EE Time. AspenCore, Inc.

The 32-bit RISC processors can be broken down into microcontrollers, host processors, embedded processors and I/O processors.

- ^ "Microprocessors From the Programmer's Perspective" by Andrew Schulman 1990

- ^ Dowd, Kevin; Loukides, Michael K. (1993). High Performance Computing. O'Reilly. ISBN 1565920325.

- ^ Vincent, James (9 مارس 2017). "Microsoft unveils new ARM server designs, threatening Intel's dominance". The Verge. Retrieved 12 مايو 2017.

- ^ Russell, John (31 مايو 2016). "Cavium Unveils ThunderX2 Plans, Reports ARM Traction is Growing". HPC Wire. Retrieved 8 مارس 2017.

- ^ AMD's first ARM-based processor, the Opteron A1100, is finally here, ExtremeTech, 2016-01-14, http://www.extremetech.com/extreme/221282-amds-first-arm-based-processor-the-opteron-a1100-is-finally-here, retrieved on 2016-08-14

- ^ Feldman, Michael (18 يناير 2017). "Cray to Deliver ARM-Powered Supercomputer to UK Consortium". Top500.org. Retrieved 12 مايو 2017.

- ^ "Microsoft is bringing Windows desktop apps to mobile ARM processors". The Verge. Vox Media. 8 ديسمبر 2016. Retrieved 8 ديسمبر 2016.

- ^ "How x86 emulation works on ARM". Microsoft Docs. 15 فبراير 2018.

- ^ "Apple announces Mac transition to Apple silicon" (Press release). Cupertino, California: Apple Inc. 22 يونيو 2020. Retrieved 18 يوليو 2020.

- ^ Srinivasan, Sundar (2009). "Intel x86 Processors – CISC or RISC? Or both??".

- ^ Carter, Nicholas P. (2002). Schaum's Outline of Computer Architecture. p. 96. ISBN 0-07-136207-X.

- ^ Jones, Douglas L. (2000). "CISC, RISC, and DSP Microprocessors" (PDF).

- ^

Singh, Amit. "A History of Apple's Operating Systems".

the line between RISC and CISC has been growing fuzzier over the years

- ^ "Top 500 The List: November 2018". TOP 500. Retrieved 22 نوفمبر 2018.

- ^ Dandamudi 2005, pp. 121–123

- ^ DeAngelis, Marc (22 يونيو 2020). "Apple starts its two-year transition to ARM this week". Engadget. Retrieved 24 أغسطس 2020.

Apple has officially announced that it will be switching from Intel processors to its own ARM-based, A-series chips in its Mac computers.

- ^ Bennett, Amy (2005). "Apple shifting from PowerPC to". Computerworld. Retrieved 24 أغسطس 2020.

وصلات خارجية

- "RISC vs. CISC". RISC Architecture. Stanford University. 2000.

- "What is RISC". RISC Architecture. Stanford University. 2000.

- Savard, John J. G. "Not Quite RISC". Computers.

- قالب:Cite newsgroup

- Short description with empty Wikidata description

- Articles with hatnote templates targeting a nonexistent page

- Articles with redirect hatnotes needing review

- Use dmy dates from August 2016

- Wikipedia articles that are too technical from October 2016

- Articles needing expert attention from October 2016

- مقالات فيها عبارات متقادمة منذ يونيو 2020

- جميع المقالات التي فيها عبارات متقادمة

- Articles needing additional references from March 2012

- All articles needing additional references

- Articles with unsourced statements from June 2011

- مقالات فيها عبارات متقادمة منذ نوفمبر 2018

- رتب الحواسب

- Instruction set architectures